|

詳細情報 |

|||

| メモリタイプ: | 揮発性 | メモリ形式: | DRAM |

|---|---|---|---|

| テクノロジー: | SDRAM - DDR3L | メモリサイズ: | 2Gbit |

| 記憶 の 組織: | 128M x 16 | メモリインターフェース: | パラレル |

| 時計の周波数: | 800 MHz | アクセス時間: | 13.75 ns |

製品の説明

MT41K128M16JT-125 AAT:K SDRAM - DDR3LメモリIC 2Gbit パラレル800 MHz 13.75 ns

仕様 MT41K128M16JT-125 AAT:K

| タイプ | 記述 |

| カテゴリー | 集積回路 (IC) |

| 記憶力 | |

| 記憶力 | |

| Mfr | マイクロン・テクノロジー株式会社 |

| シリーズ | 自動車,AEC-Q100 |

| パッケージ | トレー |

| メモリタイプ | 揮発性 |

| メモリ形式 | DRAM |

| テクノロジー | SDRAM - DDR3L |

| メモリサイズ | 2Gbit |

| 記憶 の 組織 | 128M × 16 |

| メモリインターフェース | パラレル |

| 時計の周波数 | 800 MHz |

| サイクルの時間 - 単語,ページ | - |

| アクセス時間 | 13.75 ns |

| 電圧 - 供給 | 1.283V ~ 1.45V |

| 動作温度 | -40°C ~ 105°C (TC) |

| マウントタイプ | 表面マウント |

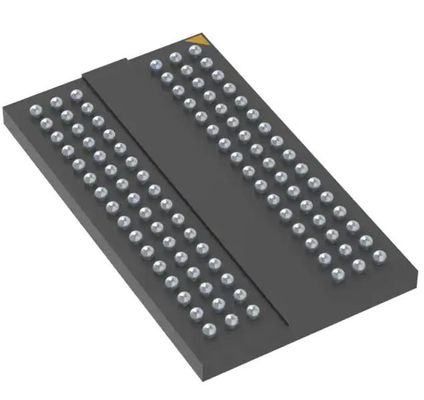

| パッケージ/ケース | 96-TFBGA |

| 供給者のデバイスパッケージ | 96-FBGA (8x14) |

| 基本製品番号 | MT41K128M16 |

特徴MT41K128M16JT-125 AAT:K

VDD = VDDQ = 1.35V (1.283 〜 1.45V)

• VDD = VDDQ = 1.5V ±0.075V に向かい合える

• 2方向データストロブ

• 8nビットプリフェッチアーキテクチャ

• 差点時計入力 (CK,CK#)

• 8つの内部銀行

• データ,ストロブ,マスク信号の名目および動的オンダイ終了 (ODT)

プログラム可能なCAS (READ) レイテンシー (CL)

• プログラム可能な CAS 添加物遅延 (AL)

プログラム可能なCAS (WRITE) レイテンシー (CWL)

固定バースト長さ (BL) 8 とバーストチョップ (BC) 4 (モードレジスタセット [MRS]経由)

選択可能なBC4またはBL8オン・ザ・フライ (OTF)

• 自動更新モード

• TC 温度範囲で最大間隔時間をリフレッシュする

40°Cから+85°Cで64ms

+85°Cから+105°Cで32ms

+105°Cから +115°Cで16ms

◎ 8ms +115°Cから+125°C

• 自動 更新 温度 (SRT)

• 自動 更新 (ASR)

• 書き直し

• 多目的登録

詳細についてMT41K128M16JT-125 AAT:K

1.35V DDR3L SDRAMデバイスは,1.5V DDR3 SDRAMデバイスの低電圧バージョンである.1.5V互換モードで動作する場合,DDR3 (1.5V) SDRAMデータシートの仕様を参照してください.

環境と輸出分類MT41K128M16JT-125 AAT:K

| ATRIBUTE について | 記述 |

| RoHS 状態 | ROHS3 に準拠 |

| 湿度感度レベル (MSL) | 3 (168 時間) |

| REACH ステータス | REACH 影響を受けない |

| ECCN | EAR99 |

| HTSUS | 8542.32.0036 |

![]()