|

詳細情報 |

|||

| シリーズ: | i.MX53 | パッケージ: | 皿 |

|---|---|---|---|

| プロダクト状態: | 時代遅れ | 中心プロセッサ: | ARM® Cortex®-A8 |

| 中心/バス幅の数: | 32ビット1つの中心 | 速度: | 800MHz |

| 共同Processors/DSP: | マルチメディア; NEON™ SIMD | RAMのコントローラー: | LPDDR2、DDR2、DDR3 |

製品の説明

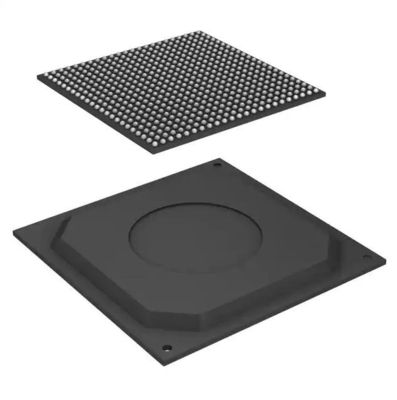

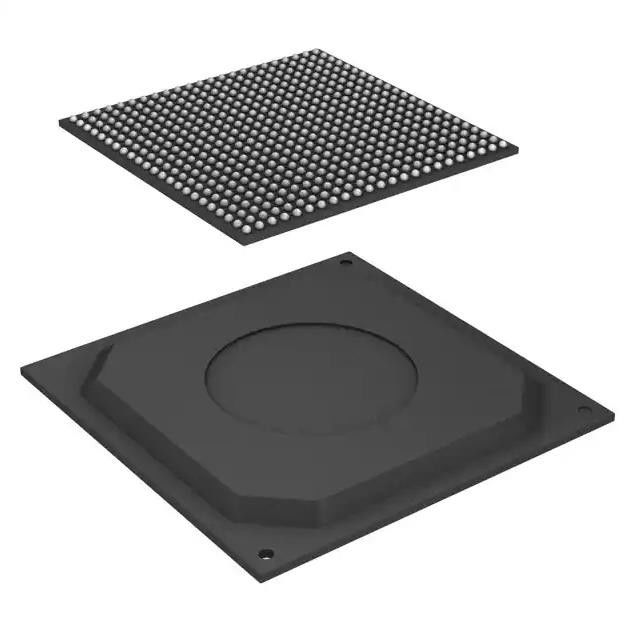

MCIMX537CVV8CのトランジスターIC破片IC MPU I.Mx53 800mhz 529fbga

ARM® Cortex®-A8マイクロプロセッサIC i.MX53 1中心、32ビット800MHz 529-FBGA (19x19)

MCIMX537CVV8Cの指定

| タイプ | 記述 |

| 部門 | 集積回路(IC) |

| 埋め込まれる | |

| マイクロプロセッサ | |

| Mfr | NXP USA Inc。 |

| シリーズ | i.MX53 |

| パッケージ | 皿 |

| プロダクト状態 | 時代遅れ |

| 中心プロセッサ | ARM® Cortex®-A8 |

| 中心/バス幅の数 | 32ビット1つの中心 |

| 速度 | 800MHz |

| 共同Processors/DSP | マルチメディア;NEON™ SIMD |

| RAMのコントローラー | LPDDR2、DDR2、DDR3 |

| グラフィック加速 | はい |

| 表示及びインターフェイス コントローラー | キーパッド、LCD |

| イーサネット | 10/100Mbps (1) |

| SATA | SATA 1.5Gbps (1) |

| USB | USB 2.0 (2)、USB 2.0 + PHY (2) |

| 電圧-入力/出力 | 1.3V、1.8V、2.775V、3.3V |

| 実用温度 | -40°C | 85°C (TA) |

| セキュリティ機能 | 腕TZのブーツの保証、暗号解読法、RTIC、安全なFusebox、安全なJTAGの安全な記憶、安全なRTCは、検出を弄る |

| タイプの取付け | 表面の台紙 |

| パッケージ/場合 | 529-FBGA |

| 製造者装置パッケージ | 529-FBGA (19x19) |

| 追加インターフェース | 1ワイヤー、AC'97、缶、Iの² CのIの² S、MMC/SD、SAI、SPI、SSI、UART |

| 基礎プロダクト数 | MCIMX537 |

MCIMX537CVV8Cの特徴

i.MX53マルチメディアのアプリケーション・プロセッサ(AP)はthefollowing特徴を備えている腕のプラットホームに基づいている、:

•MMU、L1指示およびL1データ隠し場所

•統一されたL2隠し場所

•中心の最高の頻度(を含むネオン、VFPv3およびL1隠し場所):800のMHz

•ネオン コプロセッサ(建築を処理するSIMD媒体)およびVFPv3を支えるベクトル浮動小数点(VFPライト)のコプロセッサ

•TrustZoneは次の部品から記憶装置成っている:

•水平に1つの隠し場所:

—指示(32 Kバイト)

—データ(32 Kバイト)

•レベル2キャッシュ:

—統一された指示およびデータ(256 Kバイト)

•レベル2の(内部)記憶:

—HAB (64 Kバイト)を含むブーツROM、

—の高速アクセスRAM (128 Kバイト)共有される内部マルチメディア/

—安全な/非セキュアのRAM (16 Kバイト)

•外的な記憶インターフェイス:

—16/32ビットDDR2-800、LV-DDR2-800またはDDR3-800 2までGbyte

—32ビットLPDDR2

—8/16ビット否定論履積SLC/MLCフラッシュ、66までのMHz、4/8/14/16ビットECC

—8/16ビット フラッシュ、PSRAMおよび細胞RAM。

—32ビット多重方式フラッシュ、PSRAM及び細胞RAM。

—8ビット非同期(DTACKモード) EIMインターフェイス。

—すべてのEIMピンは他のインターフェイス(NFCピンとのデータ)でmuxed。入力/出力のmuxing論理はシステム ブーツで第一次にmuxingとしてEIMの港を、選ぶ。

—サムスンOneNAND™はeMMCを含む否定論履積を速度を上げるまで4.4の管理し、(muxed I/Omodeで)

i.MX53システムは破片インターフェイスの次のシステムのまわりで造られる:

•64ビットAMBA AXI v1.0は腕のプラットホーム、マルチメディアの加速装置(VPU、IPU、GPU3D、GPU2Dのような)および作動する外的な記憶コントローラー(EXTMC)によって200のMHzでバス使用した。

•32ビットAMBA AHB 2.0は133のMHzで作動するバス マスター ペリフェラルの残りによってバス使用した。

•66のMHzで作動するほとんどのシステム周辺装置の制御(および遅いデータ トラヒックに)使用する32ビットIPバス周辺バス。

MCIMX537CVV8Cの適用

—1.4までMbps支える3つのI2S/SSI/AC97港音声に接続されるそれぞれ

多重交換装置

(AUDMUX) 4つの外的な港を提供する。

—5つのUART RS232の港、4.0までMbpsそれぞれ。1つは8ワイヤー、他の4を支える

サポート

4ワイヤー。

—1つのCSPIの港と2つの高速高められたCSPI (ECSPI)の港

—3 I2

Cの港、支持の400キロビット/秒

—IEEE1588 V1、10/100と迎合的であるように設計されている速いイーサネット コントローラー

Mbps

—2つのコントローラー区域ネットワーク(FlexCAN)インターフェイス、1 Mbpsそれぞれ

—ソニー フィリップス デジタル・インターフェイス(SPDIF)、RxおよびTx

—主パッドの港(KPP)

—2つのpulse-widthの変調器(PWM)

—割り込み機能のGPIO

MCIMX537CVV8Cの環境及び輸出分類

| 属性 | 記述 |

| RoHSの状態 | 迎合的なROHS3 |

| 湿気感受性のレベル(MSL) | 3 (168時間) |

| 範囲の状態 | 変化しないに達しなさい |

| ECCN | 5A992C |

| HTSUS | 8542.31.0001 |

![]()

この製品の詳細を知りたい