|

詳細情報 |

|||

| Mfr: | Digi | シリーズ: | NET+ARM® |

|---|---|---|---|

| パッケージ: | 皿 | プロダクト状態: | ない新しい設計のために |

| プログラム可能なDigiキー: | 確認されない | 適用: | ネットワーク プロセッサ |

| 中心プロセッサ: | ARM9® | プログラム記憶タイプ: | 外的なプログラム記憶 |

製品の説明

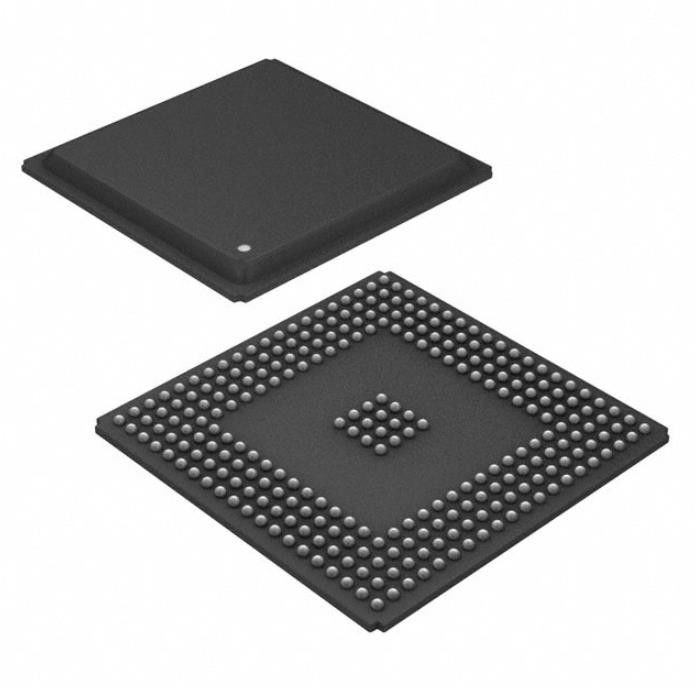

NS9360B-0-C177 タンタルチップコンデンサ NS9360b-0-C177 602-1425-Nd

IC ARM9 マイクロプロセッサ 272BGA

仕様NS9360B-0-C177

| タイプ | 説明 |

| カテゴリー | 集積回路 (IC) |

| 埋め込み | |

| 特定用途向けマイクロコントローラー | |

| 製造元 | デジ |

| シリーズ | NET+ARM® |

| パッケージ | トレイ |

| 製品の状態 | 新しいデザインは不可 |

| Digi-Key でプログラム可能 | 検証されていない |

| アプリケーション | ネットワークプロセッサ |

| コアプロセッサ | ARM9® |

| プログラムメモリの種類 | 外部プログラムメモリ |

| コントローラシリーズ | - |

| RAM サイズ | 外部の |

| インターフェース | EBI/EMI、イーサネット、DMA、I²C、IEEE 1284、LCD、SPI、UART、USB |

| I/O数 | 73 |

| 電圧 - 電源 | 1.4V~3.6V |

| 動作温度 | 0℃~70℃ |

| 取付タイプ | 表面実装 |

| パッケージ・ケース | 272-BBGA |

| サプライヤーデバイスパッケージ | 272-BGA (27x27) |

| 基本製品番号 | NS9360 |

の特徴NS9360B-0-C177

• 32ビットARM926EJ-S RISCプロセッサ

• 103 ~ 177 MHz

• インターロック付き5段パイプライン

• ハーバード大学の建築

• 8 KB 命令キャッシュと 4 KB データ キャッシュ

• 32 ビット ARM および 16 ビット Thumb 命令セット。パフォーマンス/コードのために混合可能密度のトレードオフ

• 仮想メモリベースの OS をサポートする MMULinux、WinCE/Pocket PC、VxWorks、その他

• DSP 命令拡張、改善されました除算、シングルサイクルMAC

• ARM Jazelle、1200CM (コーヒーマーク) Java アクセラレータ

• EmbeddedICE-RT デバッグユニット

• JTAGバウンダリスキャン、BSDLサポート

アプリケーション のNS9360B-0-C177

• 外部 PHY へのイーサネット MII/RMII インターフェイス

• システムメモリインターフェイス

– SDRAMへのグルーレス接続

– バッファ付き PC100 DIMM へのグルーレス接続

– SRAMへの接着剤不要の接続

– フラッシュメモリまたはROMへのグルーレス接続

• 内部 USB PHY を使用した USB ホストまたはデバイス インターフェイス

• I2Cインターフェース

• 以下と多重化された 73 個の GPIO ピン:

– 各 8 ピンのシリアル ポート 4 つ、それぞれ UART または SPI にプログラム可能

– 1284ポート

– LCDコントローラーインターフェース

環境および輸出の分類NS9360B-0-C177

| 属性 | 説明 |

| RoHS ステータス | RoHS対応 |

| 感湿性レベル (MSL) | 1 (無制限) |

| リーチステータス | REACHは影響を受けない |

| ECCN | 3A991A2 |

| HTSUS | 8542.31.0001 |

| カリフォルニア プロップ 65 | 警告情報 |

![]()

この製品の詳細を知りたい